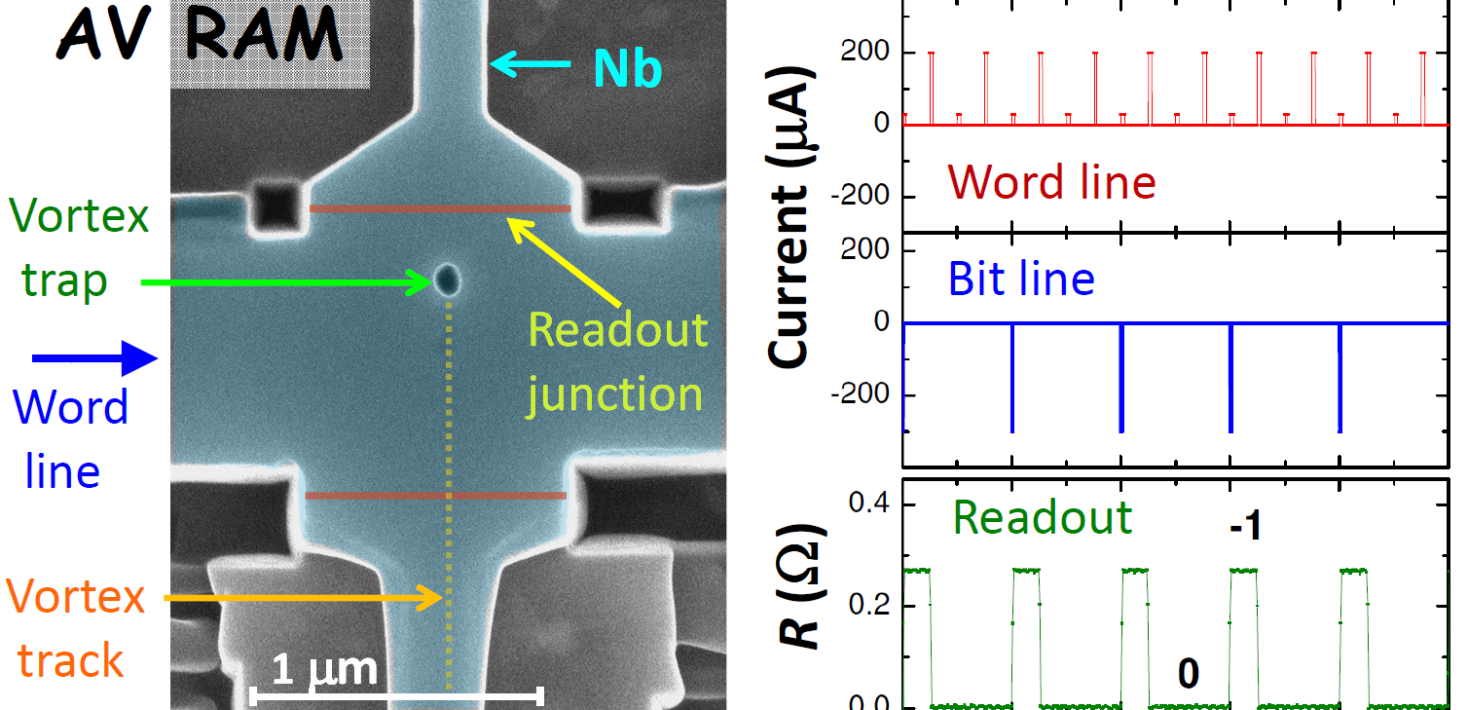

Word and bit line operation of a 1x1 μm2 superconducting vortex-based memory

The third industrial “digital” revolution is on the way. The volume of digital information, the amount of large computation facilities and the related energy consumption are growing in an explosive manner. The notorious “memory wall” problem reveals ineffectiveness of the standard processor-centered computation for processing of big data volumes and actuates the necessity of both hardware and software development for new types of in-memory computation. Simultaneously, silicon-based electronics is approaching its limits. The large resistivity of nano-scale semiconductor transistors and interconnections impedes operation speed and causes severe heat management problems. Sustainability of the present digitalization trend requires radical innovative solutions.

The development of superconducting electronics could lead to a breakthrough in future computation techniques. Major advances in superconducting quantum computing were recently achieved. However, practical calculations today are made on a classical computer and demands for digital computation capacities are growing in the explosive manner. Resistivity causes principle limitations for semiconductor electronics. It limits both the operation speed (determined by the RC time constant) and creates a problem of heat management in very-largescale-integration (VLSI) circuits. Those obstacles can be obviated by shifting to superconductors with zero resistance. The maximum operation frequency of SC electronics is determined by the energy gap, which can exceed 10 THz in high-temperature superconductors. For large data facilities shifting from semiconductors to superconductors could drastically improve both the power efficiency (by an order of magnitude) and the computation speed (by several orders of magnitude). Such perspectives reignited the interest to a classical superconducting computer.

Digital SC electronics has a long history. Rapid-single- flux-quantum (RSFQ) architecture was developed almost half a century ago. It is based on storage and manipulation of the flux quantum, Φ0, in superconducting quantum interference devices (SQUIDs). Nb-based RSFQ electronics is capable of operation at sub-THz frequencies, two orders of magnitude faster than modern computers. However, RSFQ has a major problem with scalability. The current needed for introduction of Φ0 is determined by the inductance, Λ, of the SQUID loop, I = Φ0/Λ. Upon miniaturization, Λ decreases and the operation current increases inversely proportional to the size. Therefore, RSFQ is not compatible with the VLSI technology. The main bottleneck of superconducting digital electronics is the lack of dense random-access memory (RAM). State of the art RSFQ RAM has a footprint of ∼ 100 μm2 per bit. Large sizes cause significant delay times. In fact, the speed of RSFQ is limited by delay times, rather than the energy gap. Novel approaches are needed for building a VLSI competitive superconducting electronics.

In the recent work “Word and bit line operation of a 1x1 m2 superconducting vortex-based memory” researchers from the Experimental Condensed Matter Physics group at Fysikum have demonstrated prototypes of novel vortex-based superconducting memory cells.

The key idea is to employ a quantized Abrikosov vortex as an information carrier. Vortex is the smallest magnetic object in superconductors with sizes down to 10-100 nm, which facilitates miniaturization of cells to nm-scales. Three main results were obtained. First, the scalability of vortex-based cells has been tested and it was demonstrated that such cells can be straightforwardly miniaturized to submicron sizes. Second, the importance of conscious geometrical engineering of cells was emphasized: such cells essentially are fluxonic quantum dots, for which the geometry is playing a crucial role. In the studied devices researchers have introduced an asymmetric easy track for vortex motion and have showed that it enables a controllable manipulation of vortex states.

Finally, a detailed analysis of word and bit line operation of a 1 × 1 μm2 cell was performed. High-endurance, non-volatile operation at zero magnetic field was reported. Remarkably, it was observed that the combined word and bit line threshold current was significantly reduced compared to the bare word-line operation. This could greatly improve the selectivity of individual cell addressing in a multi-cell RAM. The achieved one square micron area is an important milestone and a significant step forward towards creation of a dense cryogenic memory, says prof. Vladimir Krasnov.

More information

Word and bit line operation of a 1 × 1 μm2 superconducting vortex-based memory

Last updated: September 22, 2023

Source: Fysikum